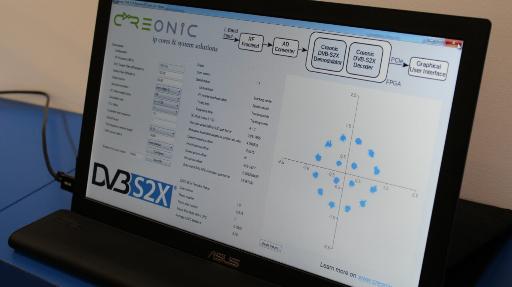

Creonic Shows Live Demo of DVB-S2X IP Cores at IBC

Kaiserslautern, Germany, Sept. 11 2014 – Creonic

GmbH, member of the DVB project, exhibits the world’s first

off-the-shelf IP cores for the new DVB-S2X standard in a live demo at

the IBC exhibition from 12th to 16th of September in Amsterdam, the

Netherlands. The live demo is shown on the DVB booth (Hall 1, Stand

1.D81) and comprises Creonic’s DVB-S2X demodulator including timing

recovery, synchronization of phase and frequency as well as LDPC and BCH

decoder for forward error correction. The IP cores are scalable for

coded throughputs of up to 800 Mbit/s and implemented in a Xilinx FPGA.

They cover the whole digital signal processing required for data

transmission or video broadcasting via DVB-S2X.

Kaiserslautern, Germany, Sept. 11 2014 – Creonic

GmbH, member of the DVB project, exhibits the world’s first

off-the-shelf IP cores for the new DVB-S2X standard in a live demo at

the IBC exhibition from 12th to 16th of September in Amsterdam, the

Netherlands. The live demo is shown on the DVB booth (Hall 1, Stand

1.D81) and comprises Creonic’s DVB-S2X demodulator including timing

recovery, synchronization of phase and frequency as well as LDPC and BCH

decoder for forward error correction. The IP cores are scalable for

coded throughputs of up to 800 Mbit/s and implemented in a Xilinx FPGA.

They cover the whole digital signal processing required for data

transmission or video broadcasting via DVB-S2X.

As a member of the DVB consortium, Creonic has followed the standardization process closely. DVB-S2X provides lower roll-off factors as well as additional modulation levels (64-APSK, 128-APSK, and 256-APSK). The DVB-S2X Forward Error Correction (FEC) has been extended to include new LDPC/BCH codes that allow more efficient use of existing satellite transmission channels.

The

Creonic DVB-S2X demodulator and decoder IP cores have been built using

the company’s proven DVB-S2 cores as a starting point, delivering the

highest possible throughput per unit area and forward error correction

performance. Both cores are supplied for FPGA and ASIC technologies, as

either pre-compiled netlists or as source code.

The

Creonic DVB-S2X demodulator and decoder IP cores have been built using

the company’s proven DVB-S2 cores as a starting point, delivering the

highest possible throughput per unit area and forward error correction

performance. Both cores are supplied for FPGA and ASIC technologies, as

either pre-compiled netlists or as source code.

Learn more about the Creonic DVB-S2X Portfolio!